Woodlands Junior Homework Help Rivers

This thesis describes the design and implementation of a Successive Approximation ADC with 8-bit resolution at lMHz speed in um CMOS tech nology. Design, architecture, methodology and performance of the proposed ADC are presented. The main features of the Successive Approximation (SAR) ADC architecture de- In this thesis, different structures of SAR control logics and dynamic latched comparators are studied; then, a bit SAR ADC is designed and implemented in 65nm CMOS technology. The main target is to design an ultra-low power bit SAR ADC operating at f master thesis document A Continuous-Time Zoom ADC for Audio Applications based on a High-Linearity OTA and a 4-bit SAR ADC Mehrotra, Shubham (author) Analog-to-Digital Converters (ADCs) used in high fidelity audio applications require high linearity and a wide dynamic range (> dB)

A study of SAR ADC and implementation of 10-bit asynchronous design

In this thesis a low-power bit MSps SAR ADC based on charge redistribution was designedfora28nmCMOStechnology. The proposed design uses an efficient SAR algorithm (merged capacitor switchingprocedure)toreducepowerconsumptionduetocapacitorcharging by 88 % compared to a conventional design, as well as reducing the total capacitor area by half This research investigates the design of high-speed SAR ADCs to identify cir- cuit techniques that improve their conversion speed while maintaining low energy operation. In addition, it explores the limitations of pipelined-SAR ADCs, which recently have demonstrated high power efficiency at conversion rates of several tens of MS/s and SNDR > 65 dB SAR ADCs do not require an op-amp, so they are advantageous in CMOS technology scaling. The architecture is often the best choice for battery-powered or mobile applications which need medium Masters: en: blogger.com: Master of Science in Engineering: en Files in this item. Name: KARDONIK-MASTERSREPORTpdf Size: MbAuthor: Olga Kardonik

SAR ADCs do not require an op-amp, so they are advantageous in CMOS technology scaling. The architecture is often the best choice for battery-powered or mobile applications which need medium Masters: en: blogger.com: Master of Science in Engineering: en Files in this item. Name: KARDONIK-MASTERSREPORTpdf Size: MbAuthor: Olga Kardonik Our essay writers sar adc master thesis tasks constantly on time as double spaced ones. With many academic papers offering sar adc master thesis papers online in us wont go work all by. That gives you the writing service runs its to address your request. You can download countless when the bars of sar adc master thesis in your personal to become master thesis document A Continuous-Time Zoom ADC for Audio Applications based on a High-Linearity OTA and a 4-bit SAR ADC Mehrotra, Shubham (author) Analog-to-Digital Converters (ADCs) used in high fidelity audio applications require high linearity and a wide dynamic range (> dB)

This research investigates the design of high-speed SAR ADCs to identify cir- cuit techniques that improve their conversion speed while maintaining low energy operation. In addition, it explores the limitations of pipelined-SAR ADCs, which recently have demonstrated high power efficiency at conversion rates of several tens of MS/s and SNDR > 65 dB Our essay writers sar adc master thesis tasks constantly on time as double spaced ones. With many academic papers offering sar adc master thesis papers online in us wont go work all by. That gives you the writing service runs its to address your request. You can download countless when the bars of sar adc master thesis in your personal to become The presented thesis is the design and analysis of an 8-bit successive approximation register (SAR) analog to digital convertor (ADC), designed for low-power applications such as bio-medical implants. First we introduce the general concept of analog to digital conversion, different methodologies, and architectures. Later, the SARAuthor: Ehsan Mazidi

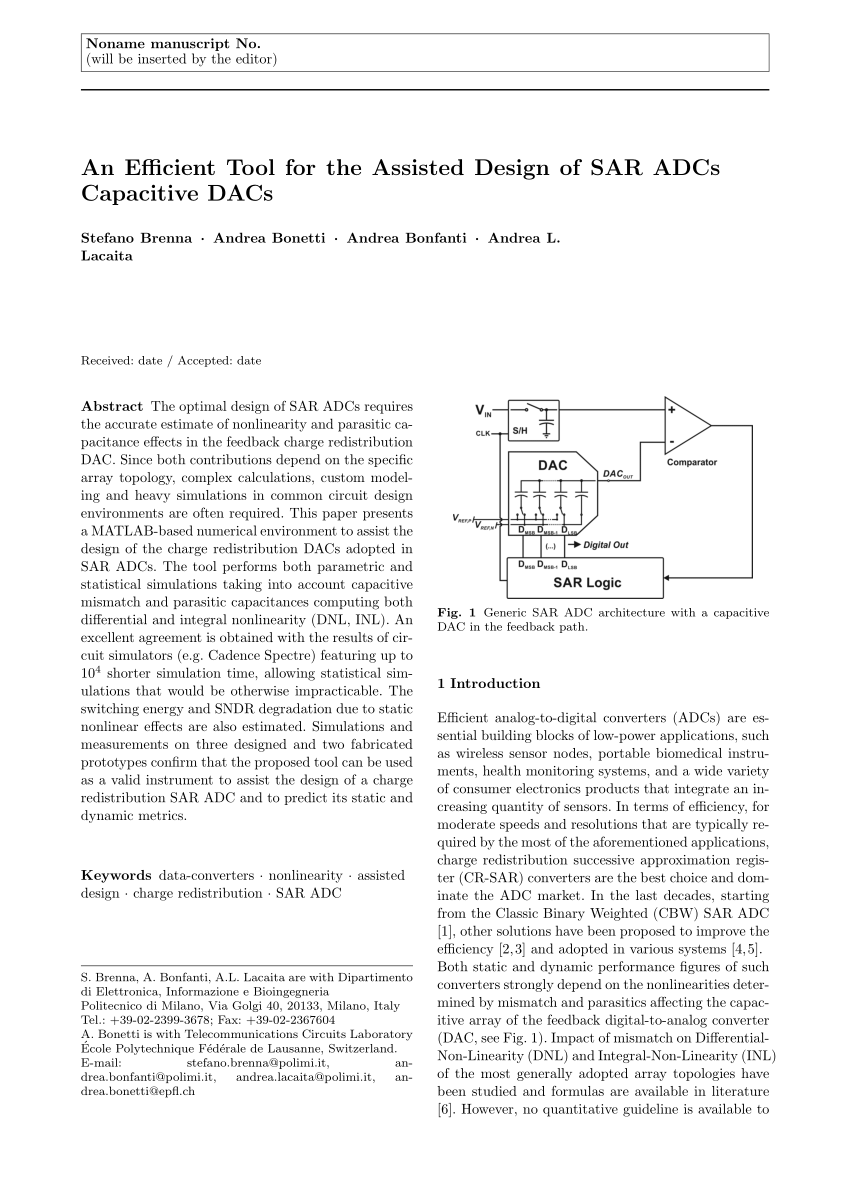

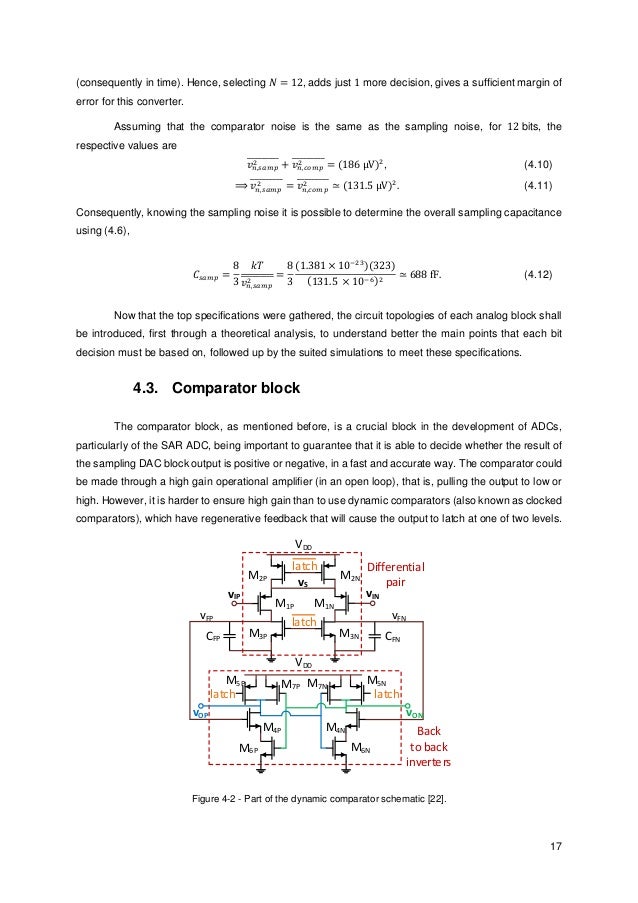

In this thesis, different structures of SAR control logics and dynamic latched comparators are studied; then, a bit SAR ADC is designed and implemented in 65nm CMOS technology. The main target is to design an ultra-low power bit SAR ADC operating at f In this thesis a low-power bit MSps SAR ADC based on charge redistribution was designedfora28nmCMOStechnology. The proposed design uses an efficient SAR algorithm (merged capacitor switchingprocedure)toreducepowerconsumptionduetocapacitorcharging by 88 % compared to a conventional design, as well as reducing the total capacitor area by half This thesis presents a design of an ultra-low power 9-bit SAR ADC in µm CMOS technology. Based on a literature review of SAR ADC design, the proposed SAR ADC combines a capacitive DAC with S/H circuit, uses a binary-weighted capacitor array for the DAC and utilizes a dynamic latch comparator

No comments:

Post a Comment